Гибридный планировщик

Из за ограниченного количества логических элементов на нашей ПЛИС, нам не удалось аппаратно реализовать планировщик задач. Поэтому использована гибридная схема, при которой планировщик задач реализован в микрокоде процессора. В систему команд процессора добавлено несколько новых инструкций для взаимодействий с планировщиком, а также добавлены некоторые аппаратные возможности для обеспечения многозадачности.

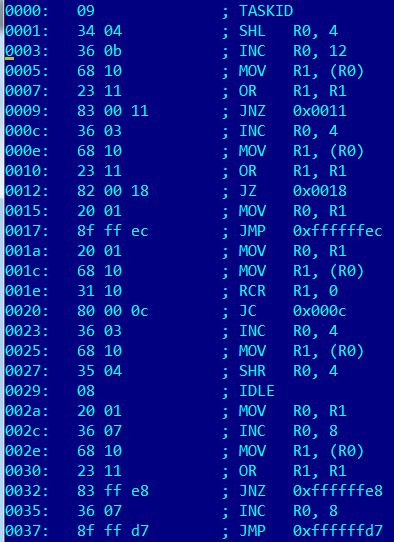

Ниже показана предварительная версия микрокода-планировщика. Вход в планировщик осуществляется по сигналу от системного таймера или инструкцией IDLE. В микрокоде планировщика использовано минимальное подмножество системы команд Everest.

Данный код использует две новые инструкции — TASKID возвращает в регистре R0 номер текущей задачи и IDLE осуществляет безусловный вход в планировщик.

Семантика инструкций TASKID и IDLE изменяется при их использовании в контексте планировщика — при использовании этих инструкций в коде планировщика, TASKID возвращает идентификатор задачи, во время исполнения которой произошёл вход в планировщик, а инструкция IDLE производит выход из планировщика и переключение на задачу, идентификатор которой задан в регистре R0, при этом задаче отводится количество тактов, заданное в регистре R1. Через заданное количество тактов сигнал от таймера произведёт вход в планировщик.

На этом рисунке показан дизассемблированный дамп планировщика

После старта процессор запускается в однозадачном режиме вплоть до инструкции IDLE — первый вход в планировщик включает многозадачный режим. Регион памяти, описывающий параметры задач, должен быть инициализирован до исполнения первой инструкции IDLE.

Обращаем ваше внимание, что это предварительная информация этапа проектирования — спецификация и её реализация могут быть изменены в любой момент без предварительного уведомления.

Оставить комментарий