Контроллер SDRAM для Марсохода

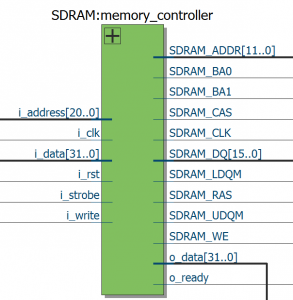

Уважаемые друзья! Мы потратили много времени в поисках подходящиего контроллера для нашей SoC и в результате решили реализовать его самостоятельно, взяв за основу спецификацию на микросхему MT48LC4M16A2-75 компании Micron. Вот какое устройство у нас получилось:

Мы реализовали 32-х битную шину данных (i_data — используется для записи данных в память, o_data — для чтения данных из памяти). Выход o_ready сигнализирует о готовности выполнения предыдущей операции и готовности принять новую команду.

Вход i_strobe сигнализирует о передаче команды контроллеру — в случае, если совместно с сигналом i_strobe подан сигнал i_write, производится запись в память данных с входный шины i_data по адресу, заданному значением на шине i_address.

Если в момент сигнала i_strobe сигнал i_write не активен, то происходит чтение данных по адресу, заданному значением на шине i_address. Считанные данные будут доступны на шине o_data при устрановке сигнала o_ready.

Сигнал i_rst используется для сброса и инициализации контроллера и микросхемы SDRAM.

Сигнал i_clk используется для тактирования контроллера и микросхемы SDRAM.

Выводы, название которых начинается со строки SDRAM_, должны быть назначены на ножки ПЛИС, подключенные к микросхеме SDRAM на плате Марсоход.

Теперь немного о временных характеристиках. Возможны три варианта задержки после поступления команды записи или чтения.

- Минимальная задержка записи/чтения 32-х разрядоного слова достигается при операциях в пределах одной строки — операция занимает 4 такта.

- Задержка в ситуации, когда в процессе доступа изменяется строка -в этом случае операция потребует 8 тактов для записи или чтения 32-х битного слова.

- Худшим случаем задержки является вариант, при котором текущая операция откадывается до завершения «рефреша» памяти и максимальное время задержки доступа к памяти может составить до 16 тактов.

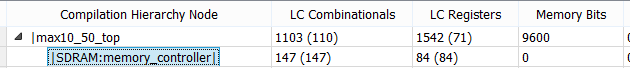

Ниже показано количество занимаемых контроллером ресурсов ПЛИС.

Фрагмент отчёта «Resource Utilization by Entity»

Схематика нашего контроллера распространяется при условии одновременного выполнения двух лицензий — Xameleon Green и Xameleon Yellow. Ознакомтесь с ними перед использованием нашего решения.

Если вы принимаете условия этих лицензий, то скачать исходный код SDRAM контроллера можно по следующей ссылке:

Скачать исходный код SDRAM контроллера для платы Марсоход

Обращаем ваше внимание на то, что мы не несём никакой ответственности за любые последствия, вызванные использованием нашего контроллера. Также мы:

- не утверждаем что контроллер не содержит ошибок;

- не утверждаем что максимально оптимально использовали возможности SDRAM;

- открыты для общения и с радостью выслушаем замечания, багрепорты и предложения по улучшению контроллера.

Размещённая на этой странице информация может быть изменена или удалена без предварительного уведомления.

Оставить комментарий