Добро пожаловать на сайт разработчиков процессора Everest!

Добро пожаловать на сайт разработчиков процессора Everest!

Мы — команда энтузиастов, работающая над созданием оригинального микропроцессора со встроенным аппаратным планировщиком.

Наша цель — создать микропроцессор для использования в проекте Хамелеон.

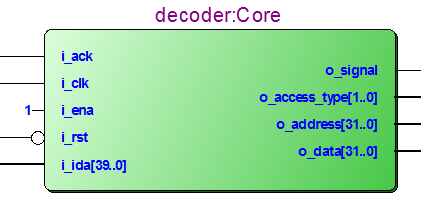

32-х битное ядро «Эверест» использует собственную систему команд основанную на архитектуре Complex Instruction Set Computing (CISC). Ядро показано на следующем рисунке:

32-х битное ядро «Эверест» имеет следующие характеристики:

- Система команд использует принципы частотного кодирования, при котором наиболее часто используемые инструкции кодируются меньшим числом байт.

- Максимальный размер команды — 40 бит, что позволяет одной инструкцией загрузить константу в регистр. Выбор 40-битной инструкции за один такт осуществляется с помощью 2-х портовой кэш памяти.

- Ядро использует 16 равноправных 32-х битных регистров общего назначения. Один из этих регистров используется так же для хранения адреса возврата из подпрограммы. Отвественность за его сохранение и восстановление лежит на программисте и компиляторах.

- Система команд использует позиционно-независимые переходы — для условных и безусловных переходов и вызовов подпрограмм используется смещение относительно текущей команды. Аналогичный принцип используется при загрузке указателей на статические константы и переменные — адрес таких структур данных помещается в регистр с учётом смещения относительно текущей инстукции.

- Система команд ядра «Эверест» легко расширяема, а её разбор прост и не требует большго количества логических элеиентов.

- Вычислительное ядро может быть использовано как самостоятельно в виде микроконтроллера, так и совместно с аппаратным планировщиком, являясь при этом устройством, аппаратно реализующим базовые примитивы микроядерной операционной системы.

Аппаратный планировщик управляет одним или несколькими вычислительными ядрами — обеспечивает переключение задач и обмен сообщениями. Исключительные ситуации и внешнние прерывания аппаратный планировщик транслирует в сообщения L4.